如何有效降低运放电路中的电源噪声

在控制工程和电子设计中,运算放大器(运放)电路的性能往往对电源噪声极为敏感。电源噪声会直接耦合到信号路径中,导致输出信号的信噪比下降、测量精度降低,甚至引发系统不稳定。特别是在使用PC电源等开关电源为精密模拟电路供电时,其固有的高频开关噪声是一个常见挑战。本文将系统地探讨降低运放电路中电源噪声的实用方法与设计原则。

1. 理解噪声来源与耦合路径

降低噪声的第一步是识别其来源。运放电路的电源噪声主要来自:

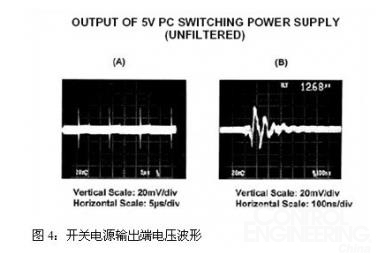

- 电源本身:如PC开关电源的纹波和开关瞬态噪声(几十kHz至数MHz)。

- 板级耦合:通过共享的电源走线或地平面,数字电路噪声耦合到模拟电源。

- 运放内部:运放的电源抑制比(PSRR)在频率升高时会下降,对高频噪声抑制能力变弱。

噪声主要通过传导和辐射两种方式进入运放。

2. 电源滤波与去耦:第一道防线

这是最直接有效的方法。

- 大容量电解电容或钽电容:在电源入口处放置(如10μF~100μF),用于滤除低频纹波,提供瞬时电流。

- 高频去耦电容:在每个运放电源引脚附近(尽可能靠近)放置一个0.1μF(100nF)的陶瓷电容,用于提供高频电流并旁路高频噪声。对于甚高频噪声,可并联一个更小值的电容(如1nF~10nF)。

- 使用π型(LC)滤波器:在开关电源输出后或运放电源入口前,串联一个铁氧体磁珠或小电感(几μH),再配合前后对地电容,构成低通滤波器,能有效抑制高频开关噪声。选择磁珠时需注意其频率阻抗特性。

3. 合理的PCB布局与接地

优秀的布局可以最小化噪声耦合。

- 模拟与数字电源分离:如果系统同时包含模拟和数字部分,应使用独立的稳压器或滤波网络为模拟运放供电,避免数字噪声通过电源线直接注入。

- 星型接地或单点接地:为模拟部分建立干净、独立的接地路径,最终在一点与数字地连接,通常连接在电源入口附近。避免模拟和数字电流在同一个地平面路径上重叠。

- 电源走线设计:使用尽可能宽而短的走线为运放供电,减少走线电感。电源线应紧邻地线或地平面,以形成小的回路面积,降低辐射和感应。

- 将敏感模拟电路远离噪声源:如远离开关电源模块、数字IC、时钟振荡器等。

4. 选择高性能的运放与电源

- 选择高PSRR的运放:查阅运放数据手册,选择在您关注频率范围内(尤其是开关电源噪声频率处)具有较高电源抑制比(PSRR)的型号。

- 使用线性稳压器(LDO):在开关电源(PC电源)后级增加一个低压差线性稳压器(LDO)为运放供电。LDO能极大抑制高频噪声,虽然效率低于开关电源,但能提供非常“安静”的电压。确保LDO本身的输出噪声和PSRR指标满足要求。

5. 屏蔽与隔离

在噪声极其严重或要求极高的场合:

- 为模拟电路部分添加金属屏蔽罩。

- 考虑使用隔离电源模块:将模拟电路的供电地与系统的其他部分进行电气隔离,阻断传导噪声路径。

6. 仿真与测量验证

在设计阶段,可以使用SPICE工具仿真电源滤波网络的效果。电路板制作完成后,必须使用示波器进行测量:

- 用示波器(建议使用带宽足够、低噪声探头)直接测量运放电源引脚上的交流成分。

- 观察采取滤波措施前后的噪声电平变化,验证设计效果。

###

降低运放电路中的电源噪声,特别是使用PC电源时,是一个系统工程。没有单一的“银弹”,而是需要结合滤波(去耦电容、LC滤波器)、隔离(LDO)、优化布局(分离、接地)和器件选择等多管齐下的策略。从噪声源头进行抑制,在传播路径上进行阻断,是达成低噪声、高精度运放电路设计目标的关键。通过审慎的设计与严格的测试,即使采用开关电源,也能为敏感的模拟电路提供足够纯净的供电环境。

如若转载,请注明出处:http://www.51313551185.com/product/12.html

更新时间:2026-03-13 01:32:00